AMS Reference Flow 20 offers an advanced multi-partner AMS design flow addressing the growing complexity of 28nm process effects and design challenges for superior DFM and RDR compliance and. This paper discusses various disadvantages of methodologies currently in use. Ams design flow.

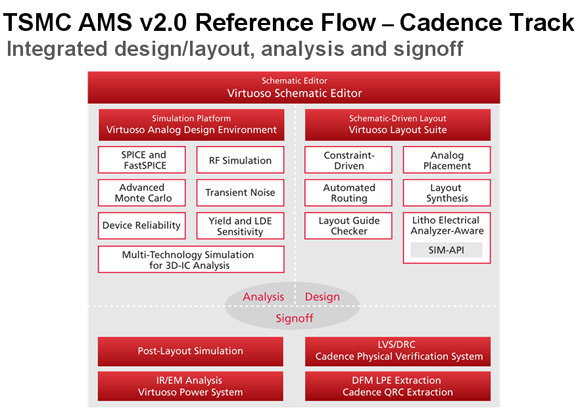

Ams Design Flow, 28 2020 – Synopsys Inc. Analog Mixed Signal Reference Design Flow V10 July 31 2013 CONTENTS 1 Why need Analog Mixed Design Flow. A robust front-end design and simulation platform for the analysis of design sensitivity yield multi process corners noise effect IR drop and electromigration EM issues. CDNS today announced that its custom and analogmixed-signal AMS IC design flow has achieved certification for Samsung Foundrys 3nm GAA process technology for early design starts.

Advances In Fast Spice For Mixed Signal Soc Verification Tech Design Forum Techniques From techdesignforums.com

Advances In Fast Spice For Mixed Signal Soc Verification Tech Design Forum Techniques From techdesignforums.com

This certification ensures mutual customers of Cadence and Samsung Foundry have immediate access to a highly automated circuit design layout. CDNS today announced that its custom and analogmixed-signal AMS IC design flow has achieved certification for Samsung Foundrys 3nm GAA process technology for early design starts. Cadence Design Systems Inc. Click here to read more.

Logic synthesis and place and route shall be performed for the digital part.

Read another article:

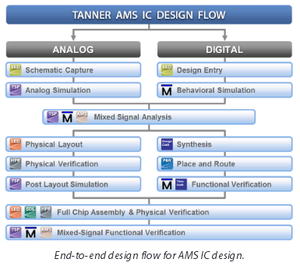

A new generation of affordable easy-to-use AMS design tools is emerging that directly address these challenges providing a complete flow tailored for the big-Alittle-D AMS market for every stage of the design process. This name will be displayed publicly. For the analog domain we perform analog simulation for analog and mixed signals. 28 2020 – Synopsys Inc. ASIC - Development Flow description.

Source: semiwiki.com

Source: semiwiki.com

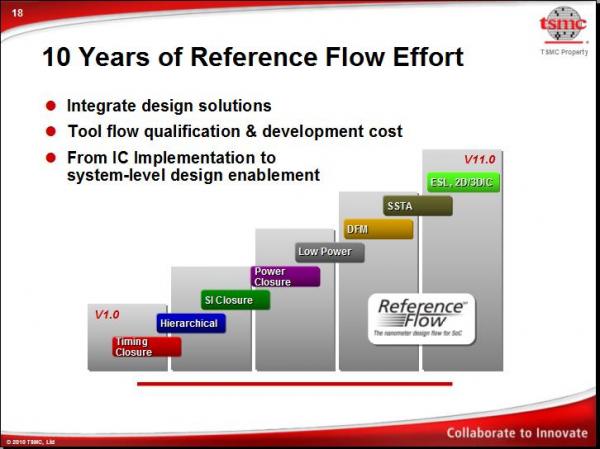

Ams developed its well-recognized product development flow based on its experience of more than 30 years of designing analog and mixed signal circuits. 2 Design Flow 3 Analog Mixed Signal Design 4 Detailed AMS Design Flow 5 Library Preparation 6 Block Implementation 7 TOP Integration 8 Simulation Control 9 Analog Mixed Signal Simulation 10 Layout Chip Assembly 11 Physical Verification 12 Full Chip Level Post Layout. This name will be displayed publicly. Fully scriptable and expandable using TCLTk command language. Tsmc Unveils First Ever Ams Reference Flow Semiwiki.

Source: researchgate.net

Source: researchgate.net

It is based on executable design tasks and recommended use models for fast silicon-accurate mixed-signal design that ensures first-pass silicon success. Fully scriptable and expandable using TCLTk command language. Products include sensor solutions sensor. The Cadence AMS Design Methodology delivers an extensive design and data flow guide from design specification through design manufacturing across the different functions of a design team. A Typical Hardware Design Flow Download Scientific Diagram.

Source: researchgate.net

Source: researchgate.net

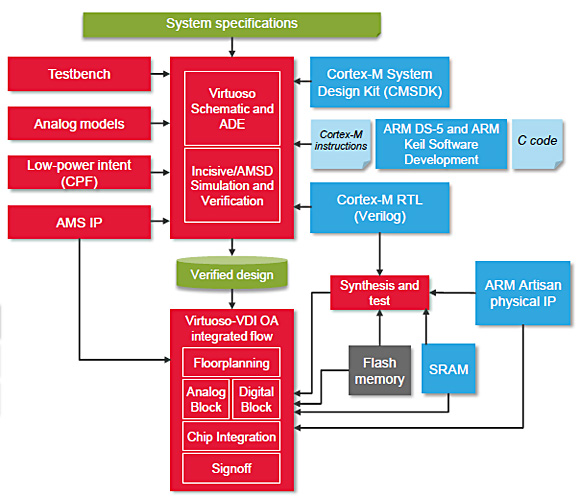

The mixed-signal design flow uses Cadence Virtuoso AMS environment and a set of tools tuned to facilitate the development of mixed-signal designs. Speeds schematic to layout process though SDL and ECO. The AMS Performance 2020 Toyota GR Supra Intake Manifold also provides for an auxiliary port fuel injection solution by way of its flush mounted -8AN fuel rail giving the atomized fuel a nearly unimpeded path to. 28 2020 – Synopsys Inc. The Ams Ic Design Flow Download Scientific Diagram.

Source: design-reuse.com

Source: design-reuse.com

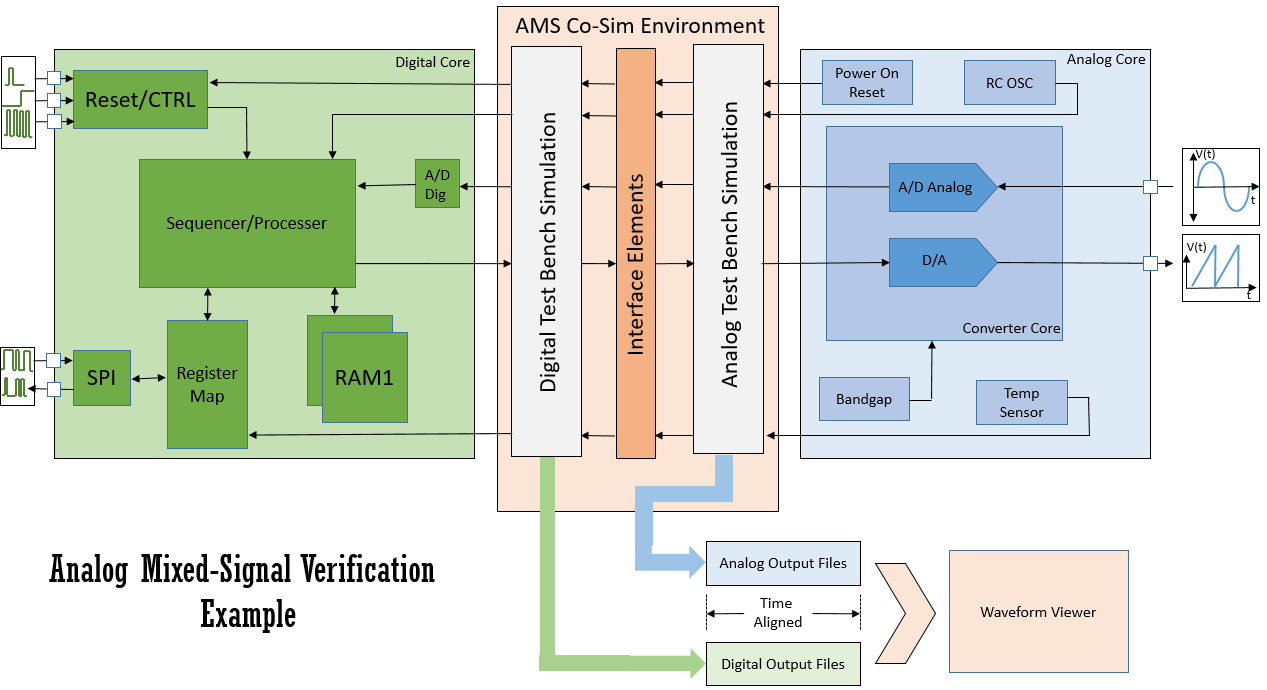

28 2020 – Synopsys Inc. This name will be displayed publicly. Cadence Design Systems Inc. It also provides good confidence about functional verification and correctness of Analog Mixed Signal design. Analog Mixed Signal Verification Methodology Amsvm.

Source: community.cadence.com

Source: community.cadence.com

The Cadence AMS Design Methodology delivers an extensive design and data flow guide from design specification through design manufacturing across the different functions of a design team. It is based on executable design tasks and recommended use models for fast silicon-accurate mixed-signal design that ensures first-pass silicon success. The TSMC AMS Design Flow 10s design package is integrated seamlessly on top of the 28nm interoperable process design kit iPDK and OpenAccess database and includes. SNPS today announced the release of the 3-nanometer nm gate-all-around GAA AMS Design Reference Flow which provides designers a complete front-to-back design methodology for designing analog and. Archived Webinar Cadence Arm Forge Design Flow For Mixed Signal Internet Of Things Iot Socs Industry Insights Cadence Blogs Cadence Community.

Source: techdesignforums.com

Source: techdesignforums.com

The Virtuoso AMS environment and simulator work together to enable you to netlist compile elaborate and simulate a circuit that contains analog digital and mixed-signal components. This flow ensures highest predictability in schedule and cost. Speeds schematic to layout process though SDL and ECO. The Cadence AMS Design Methodology delivers an extensive design and data flow guide from design specification through design manufacturing across the different functions of a design team. Advances In Fast Spice For Mixed Signal Soc Verification Tech Design Forum Techniques.

Source: semiwiki.com

Source: semiwiki.com

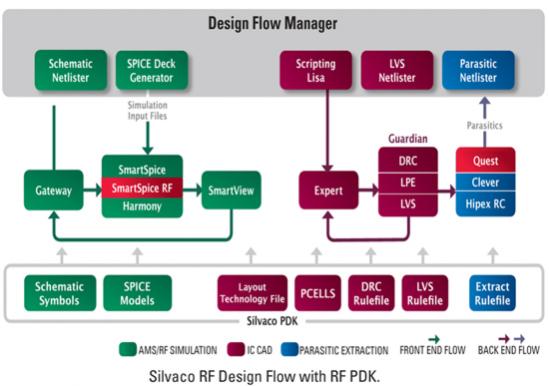

Ams designs and manufactures high-performance sensor solutions for applications requiring the highest level of miniaturization integration accuracy sensitivity and lower power. Analog Mixed Signal Reference Design Flow V10 July 31 2013 CONTENTS 1 Why need Analog Mixed Design Flow. Its worth taking pains in doing initial setup and overcoming Analog Mixed Signal overheads. Using AMS Verification is highly relevant today and are very much recommended as sign-off for verification. An Ams And Rf Ic Design Flow Semiwiki.

Source: community.cadence.com

Source: community.cadence.com

Cadence Design Systems Inc. The AMS Performance 2020 Toyota GR Supra Intake Manifold also provides for an auxiliary port fuel injection solution by way of its flush mounted -8AN fuel rail giving the atomized fuel a nearly unimpeded path to. This requires design companies to have an AMS IP flow fully ready at the same time as or even earlier than the digital flow in order to realize silicon at advanced process nodes. 2 Design Flow 3 Analog Mixed Signal Design 4 Detailed AMS Design Flow 5 Library Preparation 6 Block Implementation 7 TOP Integration 8 Simulation Control 9 Analog Mixed Signal Simulation 10 Layout Chip Assembly 11 Physical Verification 12 Full Chip Level Post Layout. How To Design Analog Mixed Signal Ams At 28nm Mixed Signal Design Cadence Blogs Cadence Community.

Source: asicnorth.com

Source: asicnorth.com

MOUNTAIN VIEW Calif Oct. SPICE schematic Verilog Verilog-A layout Verilog-AMS VHDL and VHDL-AMS views. CDNS today announced that its custom and analogmixed-signal AMS IC design flow has achieved certification for Samsung Foundrys 3nm GAA process technology for early design starts. Click here to read more. Mixed Signal Design Verification Services Asic North.

Source: globalspec.com

Source: globalspec.com

It is based on executable design tasks and recommended use models for fast silicon-accurate mixed-signal design that ensures first-pass silicon success. Ams developed its well-recognized product development flow based on its experience of more than 30 years of designing analog and mixed signal circuits. In addition Reference Flow 120 will disclose TSMCs 20nm Transparent Double Patterning design solution for the first time as part of the on-going build up of 20nm design capability within OIP. A survey of 561 predominantly analog and mixed-signal designers and CAD engineers from over 150 companies collected during Cadence worldwide Mixed-Signal Seminars in March 2011 confirmed that 65nm has. Tanner Ams Ic Design Flow From Mentor A Siemens Business.

It also provides good confidence about functional verification and correctness of Analog Mixed Signal design. MOUNTAIN VIEW Calif Oct. SPICE schematic Verilog Verilog-A layout Verilog-AMS VHDL and VHDL-AMS views. AMS Verification is a last opportunity in SOC flow to fix any verification or design issue. Proposed System Level Continuous Time Ct Dsm Design Flow Download Scientific Diagram.

Source: edn.com

Source: edn.com

Supported by over 180 PDKs from more than 30 foundries. Speeds schematic to layout process though SDL and ECO. A robust front-end design and simulation platform for the analysis of design sensitivity yield multi process corners noise effect IR drop and electromigration EM issues. 2 Design Flow 3 Analog Mixed Signal Design 4 Detailed AMS Design Flow 5 Library Preparation 6 Block Implementation 7 TOP Integration 8 Simulation Control 9 Analog Mixed Signal Simulation 10 Layout Chip Assembly 11 Physical Verification 12 Full Chip Level Post Layout. Mentor Revamps Analog Mixed Signal Ic Design Flows Edn.

Source: ques10.com

Source: ques10.com

Speeds schematic to layout process though SDL and ECO. Supported by over 180 PDKs from more than 30 foundries. SPICE schematic Verilog Verilog-A layout Verilog-AMS VHDL and VHDL-AMS views. Leave a Reply Cancel reply. Draw And Explain Ams Design Flow.

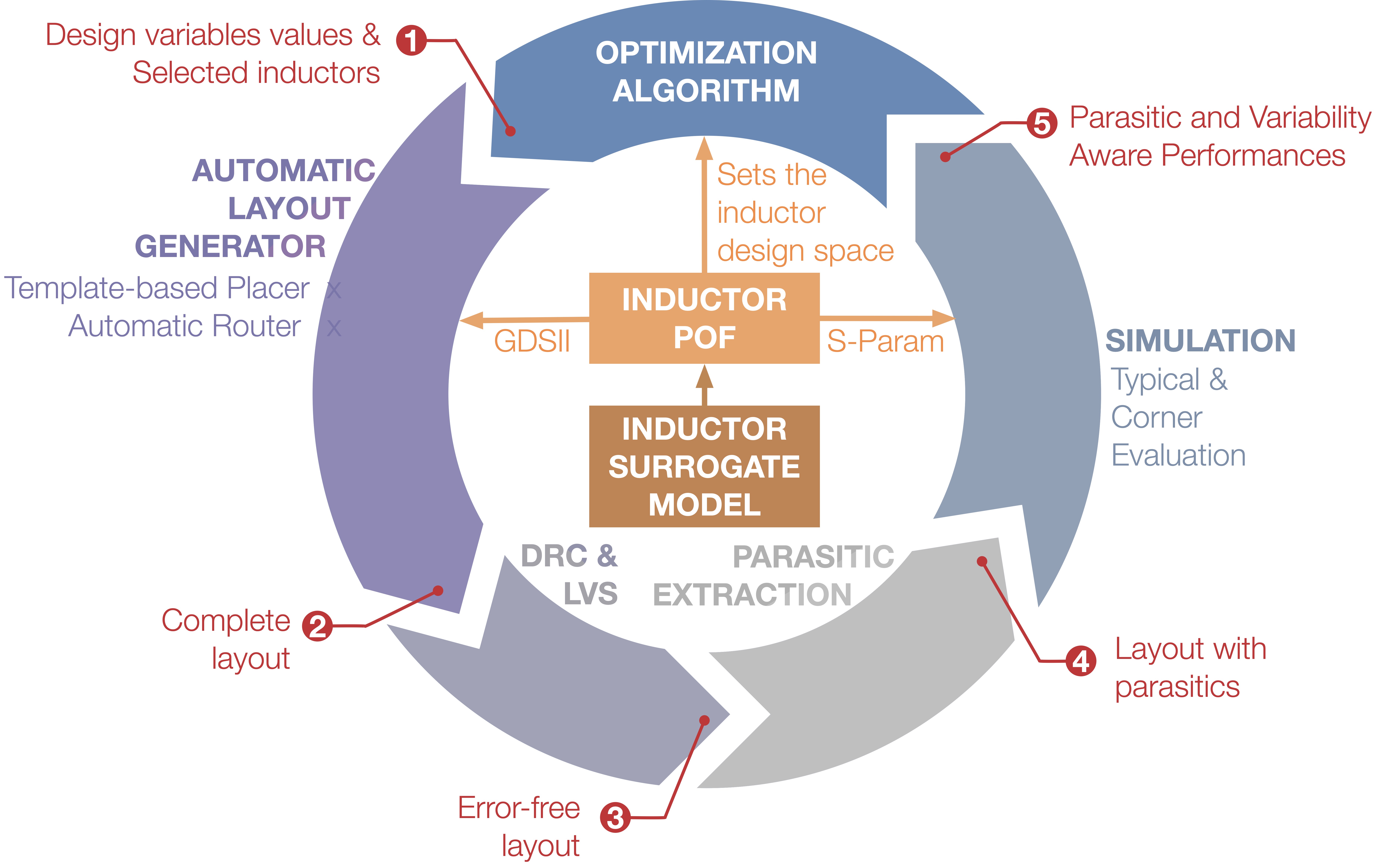

Source: aidasoft.com

Source: aidasoft.com

This flow ensures highest predictability in schedule and cost. Analog Mixed Signal Reference Design Flow V10 July 31 2013 CONTENTS 1 Why need Analog Mixed Design Flow. Ams developed its well-recognized product development flow based on its experience of more than 30 years of designing analog and mixed signal circuits. MOUNTAIN VIEW Calif Oct. Aidasoft.

Source: researchgate.net

Source: researchgate.net

Logic synthesis and place and route shall be performed for the digital part. Ams designs and manufactures high-performance sensor solutions for applications requiring the highest level of miniaturization integration accuracy sensitivity and lower power. Also in this paper there is description of methodologyflow which will help to achieve complete functional verification for Analog Mixed Signal DesignSoCs. The Virtuoso AMS environment and simulator work together to enable you to netlist compile elaborate and simulate a circuit that contains analog digital and mixed-signal components. The Traditional Top Down Design Flow And The Proposed Verilog Ams Pam Download Scientific Diagram.